## **User's Manual**

# 78K/0S Series

8-Bit Single-Chip Microcontroller

**Instructions**

Common to 78K/0S Series

Document No. U11047EJ3V0UMJ1 (3rd edition)

Date Published November 2000 N CP(K)

### [MEMO]

#### NOTES FOR CMOS DEVICES -

#### (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

#### **EEPROM** is a trademark of NEC Corporation.

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

The following products are manufactured and sold based on a license contract with CP8 Transac regarding the EEPROM microcontroller patent.

These products cannot be used for an IC card (SMART CARD).

Applicable products: μPD789146, 789156, 789197AY, 789217AY Subseries

Purchase of NEC  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Rights to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Applicable products: µPD789197AY, 789217AY Subseries

- The information in this document is current as of March, 1999. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data

books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products

and/or types are available in every country. Please check with an NEC sales representative for

availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of

third parties by or arising from the use of NEC semiconductor products listed in this document or any other

liability arising from the use of such products. No license, express, implied or otherwise, is granted under any

patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of customer's equipment shall be done under the full

responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third

parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

- "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

- (Note)

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4

### **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.l.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### **NEC Electronics (Germany) GmbH**

Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

#### **NEC Electronics (France) S.A.**

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### **NEC Electronics (France) S.A.**

Madrid Office Madrid, Spain Tel: 91-504-2787 Fax: 91-504-2860

#### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### **NEC Electronics Singapore Pte. Ltd.**

United Square, Singapore Tel: 65-253-8311

Fax: 65-250-3583

### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### **NEC do Brasil S.A.**

Electron Devices Division Guarulhos-SP Brasil Tel: 55-11-6462-6810 Fax: 55-11-6462-6829

J00.7

#### **MAJOR REVISIONS IN THIS EDITION**

| Page       | Contents                                                                                                                                                                                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout | <ul> <li>Addition of the following target products         μPD789046, 789104, 789114, 789124, 789134, 789146, 789156, 789167, 789177, 789197AY,         789217AY, 789407A, 789417A, and 789842 Subseries</li> </ul> |

|            | <ul> <li>Deletion of the following target products</li> <li>μPD789407, 789417, and 789806Y Subseries</li> </ul>                                                                                                     |

| p. 52      | Modification of MOV PSW, #byte instruction code                                                                                                                                                                     |

| p. 52      | Modification of MOVW rp, AX instruction code                                                                                                                                                                        |

| p. 54      | Modification of XOR A, r instruction code                                                                                                                                                                           |

| p. 54      | Modification of CMP A, r instruction code                                                                                                                                                                           |

The mark ★ shows major revised points.

#### INTRODUCTION

#### Readers

This manual is intended for users who wish to understand the functions of 78K/0S Series products and to design and develop its application systems and programs.

#### 78K/0S Series products

•  $\mu$ PD789014 Subseries:  $\mu$ PD789011, 789012, 78P9014

• μPD789026 Subseries: μPD789022, 789024, 789025, 789026, 78F9026

•  $\mu$ PD789046 Subseries Note:  $\mu$ PD789046, 78F9046

• μPD789104 Subseries:  $\mu$ PD789101, 789102, 789104

• *μ*PD789114 Subseries:  $\mu$ PD789111, 789112, 789114, 78F9116

• μPD789124 Subseries Note: μPD789121, 789122, 789124

μPD789134 Subseries Note:  $\mu$ PD789131, 789132, 789134, 78F9136

• μPD789146 Subseries Note: μPD789144, 789146

• μPD789156 Subseries Note: μPD789154, 789156, 78F9156

• μPD789167 Subseries Note: μPD789166, 789167

• μPD789177 Subseries Note: μPD789176, 789177, 78F9177

• μPD789197AY Subseries Note: μPD789196AY, 789197AY, 78F9197AY

μPD789217AY Subseries Note: μPD789216AY, 789217AY, 78F9217AY

• *μ*PD789407A Subseries: μPD789405A, 789406A, 789407A

• *μ*PD789417A Subseries: μPD789415A, 789416A, 789417A, 78F9418A

• *μ*PD789800 Subseries: μPD789800, 78F9801

$\mu$ PD789841, 789842, 78F9842 μPD789842 Subseries Note:

Note Under development

#### **Purpose**

This manual is intended for users to understand the instruction functions of 78K/0S Series products.

#### Organization

The contents of this manual are broadly divided into the following.

- CPU functions

- Instruction set

- · Explanation of instructions

How to read this manual It is assumed that the reader of this manual has general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

- To check the details of the functions of an instruction whose mnemonic is known:

- → See APPENDICES A and B INSTRUCTION INDEX.

- To check an instruction whose mnemonic is not known but whose general function is known:

- → Check the mnemonic in CHAPTER 4 INSTRUCTION SET, then the functions in CHAPTER 5 EXPLANATION OF INSTRUCTIONS.

- To understand the overall functions of the 78K/0S Series products instructions in general:

- → Read this manual in the order of the CONTENTS.

• To learn the hardware functions of the 78K/0S Series products:

→ Refer to the user's manual for each product (see **Related documents**).

**Conventions** Data significance: Higher digits on the left and lower digits on the right

**Note:** Footnote for item marked with **Note** in the text

Caution: Information requiring particular attention

Remark:

Supplementary information

Numeral representation:

Binary.....xxx or xxxxB

Decimal .....××××

Hexadecimal ....×××H

#### **★ Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

#### o Document common to 78K/0S Series

| Document Name              | Document Number |          |

|----------------------------|-----------------|----------|

|                            | English         | Japanese |

| User's Manual Instructions | This manual     | U11047J  |

#### o Individual documents

#### • μPD789014 Subseries

| Document Name                          | Document Number |          |

|----------------------------------------|-----------------|----------|

|                                        | English         | Japanese |

| μPD789011, 789012 Data Sheet           | U11095E         | U11095J  |

| μPD78P9014 Data Sheet                  | U10912E         | U10912J  |

| $\mu$ PD789014 Subseries User's Manual | U11187E         | U11187J  |

#### • μPD789026 Subseries

| Document Name                                | Document Number |          |

|----------------------------------------------|-----------------|----------|

|                                              | English         | Japanese |

| μPD789022, 789024, 789025, 789026 Data Sheet | U11715E         | U11715J  |

| μPD78F9026 Data Sheet                        | U11858E         | U11858J  |

| $\mu$ PD789026 Subseries User's Manual       | U11919E         | U11919J  |

#### • μPD789046 Subseries

| Document Name                                   | Document Number |          |

|-------------------------------------------------|-----------------|----------|

|                                                 | English         | Japanese |

| $\mu$ PD789046 Preliminary Product Information  | U13380E         | U13380J  |

| $\mu$ PD78F9046 Preliminary Product Information | U13546E         | U13546J  |

| $\mu$ PD789046 Subseries User's Manual          | U13600E         | U13600J  |

#### • μPD789104 Subseries

| Document Name                          | Document Number |          |

|----------------------------------------|-----------------|----------|

|                                        | English         | Japanese |

| μPD789101, 789102, 789104 Data Sheet   | To be prepared  | U12815J  |

| $\mu$ PD789134 Subseries User's Manual | U13045E         | U13045J  |

#### • $\mu$ PD789114 Subseries

| Document Name                                                  | Document Number |          |

|----------------------------------------------------------------|-----------------|----------|

|                                                                | English         | Japanese |

| $\mu$ PD789111, 789112, 789114 Preliminary Product Information | U13013E         | U13013J  |

| $\mu$ PD78F9116 Preliminary Product Information                | U13037E         | U13037J  |

| $\mu$ PD789134 Subseries User's Manual                         | U13045E         | U13045J  |

#### • μPD789124 Subseries

| Document Name                                                  | Document Number |          |

|----------------------------------------------------------------|-----------------|----------|

|                                                                | English         | Japanese |

| $\mu$ PD789121, 789122, 789124 Preliminary Product Information | U13025E         | U13025J  |

| $\mu$ PD789134 Subseries User's Manual                         | U13045E         | U13045J  |

#### • μPD789134 Subseries

| Document Name                                                  |         | Document Number |  |

|----------------------------------------------------------------|---------|-----------------|--|

|                                                                | English | Japanese        |  |

| $\mu$ PD789131, 789132, 789134 Preliminary Product Information | U13015E | U13015J         |  |

| $\mu$ PD78F9136 Preliminary Product Information                | U13036E | U13036J         |  |

| $\mu$ PD789134 Subseries User's Manual                         | U13045E | U13045J         |  |

#### $\bullet \mu$ PD789146, 789156 Subseries

| Document Name Document Nu                                              |                | nt Number |

|------------------------------------------------------------------------|----------------|-----------|

|                                                                        | English        | Japanese  |

| $\mu$ PD789144, 789146, 789154, 789156 Preliminary Product Information | U13478E        | U13478J   |

| $\mu$ PD78F9156 Preliminary Product Information                        | To be prepared | U13756J   |

| μPD789146, 789156 Subseries User's Manual                              | U13651E        | U13651J   |

#### • μPD789167, 789177 Subseries

| Document Name                                                          | Document Number |                |

|------------------------------------------------------------------------|-----------------|----------------|

|                                                                        | English         | Japanese       |

| $\mu$ PD789166, 789167, 789176, 789177 Preliminary Product Information | To be prepared  | U14017J        |

| $\mu$ PD78F9177 Preliminary Product Information                        | To be prepared  | U14022J        |

| $\mu$ PD789177 Subseries User's Manual                                 | To be prepared  | To be prepared |

#### • μPD789197AY Subseries

| Document Name                                              |         | Document Number |  |

|------------------------------------------------------------|---------|-----------------|--|

|                                                            | English | Japanese        |  |

| $\mu$ PD789196AY, 789197AY Preliminary Product Information | U13853E | U13853J         |  |

| μPD78F9197Y Preliminary Product Information                | U13224E | U13224J         |  |

| $\mu$ PD789217Y Subseries User's Manual                    | U13186E | U13186J         |  |

#### • μPD789217AY Subseries

| Document Name                                            | Document Number |          |

|----------------------------------------------------------|-----------------|----------|

|                                                          | English         | Japanese |

| $\mu$ PD789216Y, 789217Y Preliminary Product Information | U13196E         | U13196J  |

| $\mu$ PD78F9217Y Preliminary Product Information         | U13205E         | U13205J  |

| $\mu$ PD789217Y Subseries User's Manual                  | U13186E         | U13186J  |

#### • μPD789407A, 789417A Subseries

| Document Name                                                      | Documer        | Document Number |  |  |

|--------------------------------------------------------------------|----------------|-----------------|--|--|

|                                                                    | English        | Japanese        |  |  |

| μPD789405A, 789406A, 789407A, 789415A, 789416A, 789417A Data Sheet | To be prepared | U14024J         |  |  |

| μPD78F9418A Data Sheet                                             | To be prepared | To be prepared  |  |  |

| μPD789407A, 789417A Subseries User's Manual                        | To be prepared | U13952J         |  |  |

#### • $\mu$ PD789800 Subseries

| Document Name                                   | Document Number |          |

|-------------------------------------------------|-----------------|----------|

|                                                 | English         | Japanese |

| μPD789800 Data Sheet                            | U12627E         | U12627J  |

| $\mu$ PD78F9801 Preliminary Product Information | U12626E         | U12626J  |

| $\mu$ PD789800 Subseries User's Manual          | U12978E         | U12978J  |

#### • μPD789842 Subseries

| Document Name                                          | Document Number |          |  |

|--------------------------------------------------------|-----------------|----------|--|

|                                                        | English         | Japanese |  |

| $\mu$ PD789841, 789842 Preliminary Product Information | U13790E         | U13790J  |  |

| $\mu$ PD78F9842 Preliminary Product Information        | U13901E         | U13901J  |  |

| $\mu$ PD789842 Subseries User's Manual                 | U13776E         | U13776J  |  |

Caution The above documents are subject to change without prior notice. Be sure to use the latest version document when starting design.

#### **CONTENTS**

| CHAPT | ER1 N   | MEMORY SPACE                                   | 15 |

|-------|---------|------------------------------------------------|----|

| 1.1   | Memo    | ory Space                                      | 15 |

| 1.2   | Intern  | al Program Memory (Internal ROM) Space         | 15 |

| 1.3   | Vecto   | r Table Area                                   | 17 |

| 1.4   | CALL    | T Instruction Table Area                       | 20 |

| 1.5   | Intern  | al Data Memory Space                           | 20 |

| 1.6   | Specia  | al Function Register (SFR) Area                | 22 |

| СНАРТ | ER 2 F  | REGISTERS                                      | 23 |

| 2.1   | Contro  | ol Registers                                   | 23 |

|       | 2.1.1   | Program counter (PC)                           | 23 |

|       | 2.1.2   | Program status word (PSW)                      | 23 |

|       | 2.1.3   | Stack pointer (SP)                             | 24 |

| 2.2   | Gener   | ral-Purpose Registers                          | 25 |

| 2.3   | Specia  | al Function Registers (SFRs)                   | 27 |

| CHAPT | ER3 A   | ADDRESSING                                     | 29 |

| 3.1   | Addre   | essing of Instruction Address                  | 29 |

|       | 3.1.1   | Relative addressing                            | 29 |

|       | 3.1.2   | Immediate addressing                           | 30 |

|       | 3.1.3   | Table indirect addressing                      | 31 |

|       | 3.1.4   | Register addressing                            | 32 |

| 3.2   | Addre   | essing of Operand Address                      | 33 |

|       | 3.2.1   | Direct addressing                              | 33 |

|       | 3.2.2   | Short direct addressing                        | 34 |

|       | 3.2.3   | Special function register (SFR) addressing     | 35 |

|       | 3.2.4   | Register addressing                            | 36 |

|       | 3.2.5   | Register indirect addressing                   | 37 |

|       | 3.2.6   | Based addressing                               | 38 |

|       | 3.2.7   | Stack addressing                               | 38 |

| СНАРТ | ER 4 IN | NSTRUCTION SET                                 | 39 |

| 4.1   | Opera   | ition                                          | 40 |

|       | 4.1.1   | Operand representation and description formats | 40 |

|       | 4.1.2   | Description of operation column                | 41 |

|       | 4.1.3   | Description of flag column                     | 41 |

|       | 4.1.4   | Description of clock column                    | 42 |

|       | 4.1.5   | Operation list                                 | 43 |

|       | 4.1.6   | Instruction list by addressing                 | 48 |

| 4.2   | Instru  | ction Codes                                    | 51 |

|       | 4.2.1   | Description of instruction code table          | 51 |

|       | 4.2.2   | Instruction code list                          | 52 |

| CHAPT | ER 5 EXPLANATION OF INSTRUCTIONS                          | 57  |

|-------|-----------------------------------------------------------|-----|

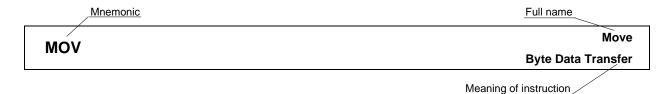

| 5.1   | 8-Bit Data Transfer Instructions                          | 59  |

| 5.2   | 16-Bit Data Transfer Instructions                         |     |

| 5.3   | 8-Bit Operation Instructions                              |     |

| 5.4   | 16-Bit Operation Instructions                             |     |

| 5.5   | Increment/Decrement Instructions                          |     |

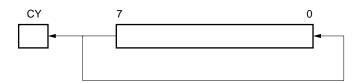

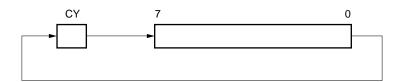

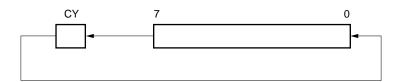

| 5.6   | Rotate Instructions                                       | 83  |

| 5.7   | Bit Manipulation Instructions                             | 88  |

| 5.8   | CALL/RETURN Instructions                                  | 92  |

| 5.9   | Stack Manipulation Instructions                           | 97  |

| 5.10  | Unconditional Branch Instruction                          |     |

| 5.11  | Conditional Branch Instructions                           | 103 |

| 5.12  | CPU Control Instructions                                  | 111 |

| APPEN | DIX A INSTRUCTION INDEX (MNEMONIC: BY FUNCTION)           | 117 |

| APPEN | DIX B INSTRUCTION INDEX (MNEMONIC: IN ALPHABETICAL ORDER) | 119 |

| APPEN | DIX C REVISION HISTORY                                    | 121 |

|       |                                                           |     |

#### **LIST OF FIGURES**

| Figure No. |                                        | Title | Page |

|------------|----------------------------------------|-------|------|

|            |                                        |       |      |

| 2-1.       | Format of Program Counter              |       | 23   |

| 2-2.       | Format of Program Status Word          |       | 23   |

| 2-3.       | Format of Stack Pointer                |       | 24   |

| 2-4.       | Data to Be Saved to Stack Memory       |       | 25   |

| 2-5.       | Data to Be Restored from Stack Memory  |       | 25   |

| 2-6.       | General-Purpose Register Configuration |       | 26   |

#### **LIST OF TABLES**

| Table | No. Tit                                                   | le                           | Page |

|-------|-----------------------------------------------------------|------------------------------|------|

| 1-1.  | Internal ROM Space of 78K/0S Series Products              |                              | 15   |

| 1-2.  | Vector Table (0000H to 0013H) (μPD789014 Subset           | ries)                        | 17   |

| 1-3.  | Vector Table (0000H to 002BH) (μPD789026 Subse            | ries)                        | 17   |

| 1-4.  | Vector Table (0000H to 0019H) (μPD789046 Subset           |                              |      |

| 1-5.  | Vector Table (0000H to 0015H) (μPD789104, 78911           | 4, 789124, 789134 Subseries) | 17   |

| 1-6.  | Vector Table (0000H to 0019H) (μPD789146, 78915           | 6 Subseries)                 | 18   |

| 1-7.  | Vector Table (0000H to 0023H) (μPD789167, 78917           | 7 Subseries)                 | 18   |

| 1-8.  | Vector Table (0000H to 0027H) (μPD789197AY, 789           | 9217AY Subseries)            | 18   |

| 1-9.  | Vector Table (0000H to 0023H) ( $\mu$ PD789407A and $\mu$ | ιPD789417A Subseries)        | 19   |

| 1-10. | Vector Table (0000H to 0019H) (μPD789800 Subset           | ries)                        | 19   |

| 1-11. | Vector Table (0000H to 0023H) (μPD789842 Subset           | ries)                        | 19   |

| 1-12. | Internal Data Memory Space of 78K/0S Series Produ         | ucts                         | 20   |

| 4-1.  | Operand Representation and Description Formats            |                              | 40   |

### [MEMO]

#### **CHAPTER 1 MEMORY SPACE**

#### 1.1 Memory Space

The 78K/0S Series product program memory map varies depending on the internal memory capacity. For details of the memory mapped address area, refer to the User's Manual of each product.

#### 1.2 Internal Program Memory (Internal ROM) Space

The 78K/0S Series product has internal ROM in the address space shown below. Program and table data, etc. are stored in ROM. This memory space is usually addressed by the program counter (PC).

Table 1-1. Internal ROM Space of 78K/0S Series Products (1/2)

|                             |         | 0.141     |           | 0.10       | 10.10     | 10.15                   | 2416                        | 22.14     |

|-----------------------------|---------|-----------|-----------|------------|-----------|-------------------------|-----------------------------|-----------|

| \C;                         | apacity | 2 Kbytes  | 4 Kbytes  | 8 Kbytes   | 12 Kbytes | 16 Kbytes               | 24 Kbytes                   | 32 Kbytes |

| \ \                         | ddress  | 0000H to  | 0000H to  | 0000H to   | 0000H to  | 0000H to                | 0000H to                    | 0000H to  |

|                             | Space   | 07FFH     | 0FFFH     | 1FFFH      | 2FFFH     | 3FFFH                   | 5FFFH                       | 7FFFH     |

| Subseries Nar               | ne 🔪    |           |           |            |           |                         |                             |           |

| $\mu$ PD789014<br>Subseries |         | μPD789011 | μPD789012 | μPD78P9014 |           |                         |                             |           |

| μPD789026<br>Subseries      |         |           | μPD789022 | μPD789024  | μPD789025 | μPD789026<br>μPD78F9026 |                             |           |

| μPD789046<br>Subseries      |         |           |           |            |           | μPD789046<br>μPD78F9046 |                             |           |

| μPD789104<br>Subseries      |         | μPD789101 | μPD789102 | μPD789104  |           |                         |                             |           |

| μPD789114<br>Subseries      |         | μPD789111 | μPD789112 | μPD789114  |           | μPD78F9116              |                             |           |

| μPD789124<br>Subseries      |         | μPD789121 | μPD789122 | μPD789124  |           |                         |                             |           |

| μPD789134<br>Subseries      |         | μPD789131 | μPD789132 | μPD789134  |           | μPD78F9136              |                             |           |

| μPD789146<br>Subseries      |         |           |           | μPD789144  |           | μPD789146               |                             |           |

| μPD789156<br>Subseries      |         |           |           | μPD789154  |           | μPD789156<br>μPD78F9156 |                             |           |

| μPD789167<br>Subseries      |         |           |           |            |           | μPD789166               | μPD789167                   |           |

| μPD789177<br>Subseries      |         |           |           |            |           | μPD789176               | μPD789177<br>μPD78F9177     |           |

| μPD789197A\<br>Subseries    | Y       |           |           |            |           | μPD789196AY             | μPD789197AY<br>μPD78F9197AY |           |

### Table 1-1. Internal ROM Space of 78K/0S Series Products (2/2)

|           | Capacity | 2 Kbytes | 4 Kbytes | 8 Kbytes  | 12 Kbytes  | 16 Kbytes   | 24 Kbytes    | 32 Kbytes   |

|-----------|----------|----------|----------|-----------|------------|-------------|--------------|-------------|

|           | Address  | 0000H to | 0000H to | 0000H to  | 0000H to   | 0000H to    | 0000H to     | 0000H to    |

|           | Space    | 07FFH    | 0FFFH    | 1FFFH     | 2FFFH      | 3FFFH       | 5FFFH        | 7FFFH       |

| Subseries | Name     |          |          |           |            |             |              |             |

| μPD78921  | 7AY      |          |          |           |            | μPD789216AY | μPD789217AY  |             |

| Subseries |          |          |          |           |            |             | μPD78F9217AY |             |

| μPD78940  | 7A       |          |          |           | μPD789405A | μPD789406A  | μPD789407A   |             |

| Subseries |          |          |          |           |            |             |              |             |

| μPD78941  | 7A       |          |          |           | μPD789415A | μPD789416A  | μPD789417A   | μPD78F9418A |

| Subseries |          |          |          |           |            |             |              |             |

| μPD78980  | 0        |          |          | μPD789800 |            | μPD78F9801  |              |             |

| Subseries |          |          |          |           |            |             |              |             |

| μPD78984  | 2        |          |          | μPD789841 |            | μPD789842   |              |             |

| Subseries |          |          |          |           |            | μPD78F9842  |              |             |

#### 1.3 Vector Table Area

The vector table area stores program start addresses to which execution branches when the  $\overline{\text{RESET}}$  signal is input or when an interrupt request is generated. Of the 16-bit address, the lower 8 bits are stored in an even address, and the higher 8 bits are stored in an odd address.

Table 1-2. Vector Table (0000H to 0013H) (μPD789014 Subseries)

| Vector Table Address | Interrupt Request | Vector Table Address | Interrupt Request |

|----------------------|-------------------|----------------------|-------------------|

| 0000H                | RESET input       | 000CH                | INTSR/INTCSI0     |

| 0004H                | INTWDT            | 000EH                | INTST             |

| 0006H                | INTP0             | 0010H                | INTTM0            |

| 0008H                | INTP1             | 0012H                | INTTM1            |

| 000AH                | INTP2             |                      |                   |

Table 1-3. Vector Table (0000H to 002BH) (μPD789026 Subseries)

| Vector Table Address | Interrupt Request | Vector Table Address | Interrupt Request |

|----------------------|-------------------|----------------------|-------------------|

| 0000H                | RESET input       | 000CH                | INTSR/INTCSI0     |

| 0004H                | INTWDT            | 000EH                | INTST             |

| 0006H                | INTP0             | 0010H                | INTTM0            |

| 0008H                | INTP1             | 0014H                | INTTM2            |

| 000AH                | INTP2             | 002AH                | INTKR             |

#### Table 1-4. Vector Table (0000H to 0019H) (μPD789046 Subseries)

| Vector Table Address | Interrupt Request | Vector Table Address | Interrupt Request |

|----------------------|-------------------|----------------------|-------------------|

| 0000H                | RESET input       | 000EH                | INTST20           |

| 0004H                | INTWDT            | 0010H                | INTWT             |

| 0006H                | INTP0             | 0012H                | INTWTI            |

| 0008H                | INTP1             | 0014H                | INTTM80           |

| 000AH                | INTP2             | 0016H                | INTTM90           |

| 000CH                | INTSR20/INTCSI20  | 0018H                | INTKR00           |

Table 1-5. Vector Table (0000H to 0015H) (μPD789104, 789114, 789124, 789134 Subseries)

| Vector Table Address | Interrupt Request | Vector Table Address | Interrupt Request |

|----------------------|-------------------|----------------------|-------------------|

| 0000H                | RESET input       | 000CH                | INTSR20/INTCSI20  |

| 0004H                | INTWDT            | 000EH                | INTST20           |

| 0006H                | INTP0             | 0010H                | INTTM80           |

| 0008H                | INTP1             | 0012H                | INTTM20           |

| 000AH                | INTP2             | 0014H                | INTAD0            |

#### Table 1-6. Vector Table (0000H to 0019H) (μPD789146, 789156 Subseries)

| Vector Table Address | Interrupt Request | Vector Table Address | Interrupt Request |

|----------------------|-------------------|----------------------|-------------------|

| 0000H                | RESET input       | 000EH                | INTST20           |

| 0004H                | INTWDT            | 0010H                | INTTM80           |

| 0006H                | INTP0             | 0012H                | INTTM20           |

| 0008H                | INTP1             | 0014H                | INTAD0            |

| 000AH                | INTP2             | 0016H                | INTLVI0           |

| 000CH                | INTSR20/INTCSI20  | 0018H                | INTEE1            |

#### \* Table 1-7. Vector Table (0000H to 0023H) (μPD789167, 789177 Subseries)

| Vector Table Address | Interrupt Request | Vector Table Address | Interrupt Request |

|----------------------|-------------------|----------------------|-------------------|

| 0000H                | RESET input       | 0012H                | INTWT             |

| 0004H                | INTWDT            | 0014H                | INTWTI            |

| 0006H                | INTP0             | 0016H                | INTTM80           |

| 0008H                | INTP1             | 0018H                | INTTM81           |

| 000AH                | INTP2             | 001AH                | INTTM82           |

| 000CH                | INTP3             | 001CH                | INTTM90           |

| 000EH                | INTSR20/INTCSI20  | 0022H                | INTAD0            |

| 0010H                | INTST20           |                      |                   |

### \* Table 1-8. Vector Table (0000H to 0027H) (μPD789197AY, 789217AY Subseries)

| Vector Table Address | Interrupt Request | Vector Table Address | Interrupt Request |

|----------------------|-------------------|----------------------|-------------------|

| 0000H                | RESET input       | 0016H                | INTTM80           |

| 0004H                | INTWDT            | 0018H                | INTTM81           |

| 0006H                | INTP0             | 001AH                | INTTM82           |

| 0008H                | INTP1             | 001CH                | INTTM90           |

| 000AH                | INTP2             | 001EH                | INTSMB0           |

| 000CH                | INTP3             | 0020H                | INTSMBOV0         |

| 000EH                | INTSR20/INTCSI20  | 0022H                | INTAD0            |

| 0010H                | INTST20           | 0024H                | INTLVI0           |

| 0012H                | INTWT             | 0026H                | INTEE1            |

| 0014H                | INTWTI            |                      |                   |

#### Table 1-9. Vector Table (0000H to 0023H) (μPD789407A and μPD789417A Subseries)

| Vector Table Address | Interrupt Request | Vector Table Address | Interrupt Request |

|----------------------|-------------------|----------------------|-------------------|

| 0000H                | RESET input       | 0014H                | INTWTI            |

| 0004H                | INTWDT            | 0016H                | INTTM00           |

| 0006H                | INTP0             | 0018H                | INTTM01           |

| 0008H                | INTP1             | 001AH                | INTTM02           |

| 000AH                | INTP2             | 001CH                | INTTM50           |

| 000CH                | INTP3             | 001EH                | INTKR00           |

| 000EH                | INTSR00/INTCSI00  | 0020H                | INTAD0            |

| 0010H                | INTST00           | 0022H                | INTCMP0           |

| 0012H                | INTWT             |                      |                   |

Table 1-10. Vector Table (0000H to 0019H) (μPD789800 Subseries)

| Vector Table Address | Interrupt Request | Vector Table Address | Interrupt Request |

|----------------------|-------------------|----------------------|-------------------|

| 0000H                | RESET input       | 000EH                | INTUSBRE          |

| 0004H                | INTWDT            | 0010H                | INTP0             |

| 0006H                | INTUSBTM          | 0012H                | INTCSI10          |

| 0008H                | INTUSBRT          | 0014H                | INTTM00           |

| 000AH                | INTUSBRD          | 0016H                | INTTM01           |

| 000CH                | INTUSBST          | 0018H                | INTKR00           |

#### Table 1-11. Vector Table (0000H to 0023H) (μPD789842 Subseries)

| Vector Table Address | Interrupt Request | Vector Table Address | Interrupt Request |

|----------------------|-------------------|----------------------|-------------------|

| 0000H                | RESET input       | 0016H                | INTST00           |

| 0004H                | INTWDT            | 0018H                | INTWT             |

| 0006H                | INTP0             | 001AH                | INTWTI            |

| 0008H                | INTP1             | 001CH                | INTTM80           |

| 000AH                | INTTM7            | 001EH                | INTTM81           |

| 000CH                | INTSER00          | 0020H                | INTTM82           |

| 000EH                | INTSR00           | 0022H                | INTAD             |

#### 1.4 CALLT Instruction Table Area

In a 64-byte address area 0040H to 007FH, the subroutine entry address of a 1-byte call instruction (CALLT) can be stored.

#### 1.5 Internal Data Memory Space

The 78K/0S Series products incorporate the following data memory:

#### (1) Internal high-speed RAM

The 78K/0S Series products incorporate internal high-speed RAM in the address space shown in Table 1-12. The internal high-speed RAM is also used as a stack memory.

#### (2) LCD display RAM ( $\mu$ PD789407A and $\mu$ PD789417A Subseries)

LCD display RAM is allocated in the area between FA00H and FA1BH.

The LCD display RAM can also be used as ordinary RAM.

#### (3) EEPROM<sup>TM</sup> ( $\mu$ PD789146, 789156, 789197AY, 789217AY Subseries)

Electrically erasable PROM (EEPROM) is allocated in the address space shown in Table 1-12. Unlike ordinary RAM, EEPROM retains the data it contains even when the power is turned off. Also, unlike EPROM, the contents of EEPROM can be erased electrically, without the need to expose the chip to

ultraviolet light.

Table 1-12. Internal Data Memory Space of 78K/0S Series Products (1/2)

| Subseries Name | Product Name | High-Speed RAM | LCD Display RAM | EEPROM |

|----------------|--------------|----------------|-----------------|--------|

| μPD789014      | μPD789011    | FE80H to FEFFH | _               | _      |

| Subseries      | μPD789012    | (128 bytes)    |                 |        |

|                | μPD78P9014   | FE00H to FEFFH |                 |        |

|                |              | (256 bytes)    |                 |        |

| μPD789026      | μPD789022    | FE00H to FEFFH | _               | _      |

| Subseries      | μPD789024    | (256 bytes)    |                 |        |

|                | μPD789025    | FD00H to FEFFH |                 |        |

|                | μPD789026    | (512 bytes)    |                 |        |

|                | μPD78F9026   |                |                 |        |

| μPD789046      | μPD789046    | FD00H to FEFFH | _               | _      |

| Subseries      | μPD78F9046   | (512 bytes)    |                 |        |

| μPD789104      | μPD789101    | FE00H to FEFFH | _               | _      |

| Subseries      | μPD789102    | (256 bytes)    |                 |        |

|                | μPD789104    |                |                 |        |

| μPD789114      | μPD789111    | FE00H to FEFFH | _               | _      |

| Subseries      | μPD789112    | (256 bytes)    |                 |        |

|                | μPD789114    |                |                 |        |

|                | μPD78F9116   |                |                 |        |

User's Manual U11047EJ3V0UM00

### Table 1-12. Internal Data Memory Space of 78K/0S Series Products (2/2)

| Subseries Name | Product Name | High-Speed RAM | LCD Display RAM | EEPROM         |

|----------------|--------------|----------------|-----------------|----------------|

| μPD789124      | μPD789121    | FE00H to FEFFH | _               | _              |

| Subseries      | μPD789122    | (256 bytes)    |                 |                |

|                | μPD789124    |                |                 |                |

| μPD789134      | μPD789131    | FE00H to FEFFH | _               | _              |

| Subseries      | μPD789132    | (256 bytes)    |                 |                |

|                | μPD789134    |                |                 |                |

|                | μPD78F9136   |                |                 |                |

| μPD789146      | μPD789144    | FE00H to FEFFH | _               | F800H to F8FFH |

| Subseries      | μPD789146    | (256 bytes)    |                 | (256 bytes)    |

| μPD789156      | μPD789154    | FE00H to FEFFH | _               | F800H to F8FFH |

| Subseries      | μPD789156    | (256 bytes)    |                 | (256 bytes)    |

|                | μPD78F9156   |                |                 |                |

| μPD789167      | μPD789166    | FD00H to FEFFH | _               | _              |

| Subseries      | μPD789167    | (512 bytes)    |                 |                |

| μPD789177      | μPD789176    | FD00H to FEFFH | _               | _              |

| Subseries      | μPD789177    | (512 bytes)    |                 |                |

|                | μPD78F9177   |                |                 |                |

| μPD789197AY    | μPD789196AY  | FD00H to FEFFH | _               | F800H to F87FH |

| Subseries      | μPD789197AY  | (512 bytes)    |                 | (128 bytes)    |

|                | μPD78F9197AY |                |                 |                |

| μPD789217AY    | μPD789216AY  | FD00H to FEFFH | _               | F800H to F87FH |

| Subseries      | μPD789217AY  | (512 bytes)    |                 | (128 bytes)    |

|                | μPD78F9217AY |                |                 |                |

| μPD789407A     | μPD789405A   | FD00H to FEFFH | FA00H to FA1BH  | _              |

| Subseries      | μPD789406A   | (512 bytes)    | (28 bytes)      |                |

|                | μPD789407A   |                |                 |                |

| μPD789417A     | μPD789415A   | FD00H to FEFFH | FA00H to FA1BH  | _              |

| Subseries      | μPD789416A   | (512 bytes)    | (28 bytes)      |                |

|                | μPD789417A   |                |                 |                |

|                | μPD78F9418A  |                |                 |                |

| μPD789800      | μPD789800    | FE00H to FEFFH | _               | _              |

| Subseries      | μPD78F9801   | (256 bytes)    |                 |                |

| μPD789842      | μPD789841    | FE00H to FEFFH | _               | _              |

| Subseries      | μPD789842    | (256 bytes)    |                 |                |

|                | μPD78F9842   |                |                 |                |

### 1.6 Special Function Register (SFR) Area

Special-function registers (SFRs) of on-chip peripheral hardware are allocated to the area FF00H to FFFFH (refer to the User's Manual of each product).

#### **CHAPTER 2 REGISTERS**

#### 2.1 Control Registers

The control registers have dedicated functions such as controlling the program sequence, statuses, and stack memory. The control registers include a program counter, program status word, and stack pointer.

#### 2.1.1 Program counter (PC)

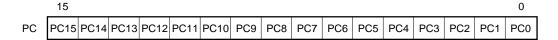

The program counter is a 16-bit register that holds the address information of the next program to be executed.

In normal operation, the PC is automatically incremented according to the number of bytes of the instruction to be fetched. When a branch instruction is executed, immediate data and register contents are set.

When the RESET signal is input, the program counter is set to the value of the reset vector table, which are located at addresses 0000H and 0001H.

Figure 2-1. Format of Program Counter

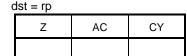

#### 2.1.2 Program status word (PSW)

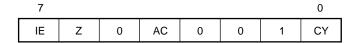

Program status word is an 8-bit register consisting of various flags to be set/reset by instruction execution.

The contents of program status word are automatically stacked when an interrupt request is generated or when the PUSH PSW instruction is executed and, are automatically reset when the RETI and POP PSW instruction are executed.

RESET input sets PSW to 02H.

Figure 2-2. Format of Program Status Word

#### (1) Interrupt enable flag (IE)

This flag controls interrupt request acknowledge operations of the CPU.

When IE = 0, all interrupts except non-maskable interrupts are disabled (DI status).

When IE = 1, interrupts are enabled (EI status). At this time, acknowledgment of interrupt requests is controlled by the interrupt mask flag for each interrupt source.

The IE flag is reset (0) when the DI instruction execution is executed or when an interrupt is acknowledged, and set (1) when the EI instruction is executed.

#### (2) Zero flag (Z)

When the operation result is zero, this flag is set (1); otherwise, it is reset (0).

#### (3) Auxiliary carry flag (AC)

If the operation result has a carry from bit 3 or a borrow to bit 3, this flag is set (1); otherwise, it is reset (0).

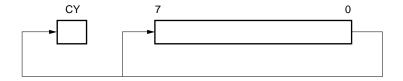

#### (4) Carry flag (CY)

This flag records an overflow or underflow upon add/subtract instruction execution. It also records the shiftout value upon rotate instruction execution, and functions as a bit accumulator during bit operation instruction execution.

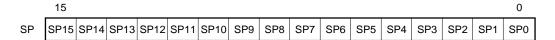

#### 2.1.3 Stack pointer (SP)

This is a 16-bit register that holds the first address of the stack area in the memory. Only the internal high-speed RAM area can be set as the stack area.

Figure 2-3. Format of Stack Pointer

The SP is decremented ahead of write (save) to the stack memory, and is incremented after read (reset) from the stack memory.

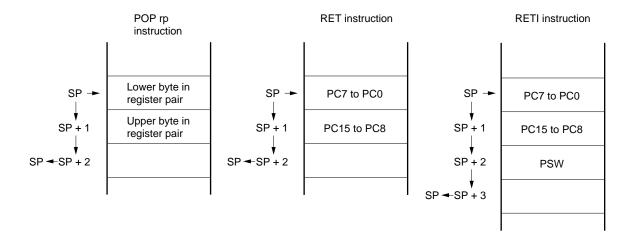

The data saved/restored as a result of each stack operation are as shown in Figures 2-4 and 2-5.

Caution Since RESET input makes the SP contents undefined, be sure to initialize the SP before executing an instruction.

PUSH rp CALL, CALLT Interrupt instruction instructions SP **-**SP - 3 SP **-**SP - 2 SP **⊸**SP – 2 **SP** - 3 PC7 to PC0 Lower byte in SP - 2SP - 2 PC7 to PC0 SP - 2 PC15 to PC8 register pair Upper byte in **SP** - 1 SP - 1 SP - 1 PC15 to PC8 **PSW** register pair SP SP SP

Figure 2-4. Data to Be Saved to Stack Memory

Figure 2-5. Data to Be Restored from Stack Memory

#### 2.2 General-Purpose Registers

The general-purpose register consists of eight 8-bit registers (X, A, C, B, E, D, L, and H).

Each register can be used as an 8-bit register, or two 8-bit registers in pairs can be used as a 16-bit register (AX, BC, DE, and HL).

Registers can be described in terms of functional names (X, A, C, B, E, D, L, H, AX, BC, DE, and HL) and absolute names (R0 to R7 and RP0 to RP3).

Figure 2-6. General-Purpose Register Configuration

#### (a) Absolute name

| 16-bit processing | 8-bit processing |

|-------------------|------------------|

| RP3               | R7               |

| KF3               | R6               |

| DDO               | R5               |

| RP2               | R4               |

| RP1               | R3               |

|                   | R2               |

| RP0               | R1               |

|                   | R0               |

| 15 0              | 7                |

### (b) Functional name

| 16-bit processing | 8-bit processing |

|-------------------|------------------|

| HL                | Н                |

| I II              | L                |

| DE                | D                |

| DE                | E                |

| BC                | В                |

| BC                | С                |

| AX                | A                |

| AA                | X                |

| 15 0              | 7 0              |

#### 2.3 Special Function Registers (SFRs)

Unlike general-purpose registers, special function registers have their own functions and are allocated to the 256-byte area FF00H to FFFFH.

A special function register can be manipulated, like a general-purpose register, by using operation, transfer, and bit manipulation instructions. The bit units in which one register is to be manipulated (1, 8, and 16) differ depending on the special function register type.

The bit unit for manipulation is specified as follows.

#### • 1-bit manipulation

Describes a symbol reserved by the assembler for the 1-bit manipulation instruction operand (sfr.bit). This manipulation can also be specified with an address.

#### · 8-bit manipulation

Describes a symbol reserved by the assembler for the 8-bit manipulation instruction operand (sfr). This manipulation can also be specified with an address.

#### • 16-bit manipulation

Describes a symbol reserved by the assembler for the 16-bit manipulation instruction operand. When addressing an address, describe an even address.

For details of the special function registers, refer to the User's Manual of each product.

### [MEMO]

#### **CHAPTER 3 ADDRESSING**

#### 3.1 Addressing of Instruction Address

An instruction address is determined by the program counter (PC) contents. The PC contents are normally incremented (+1 per byte) automatically according to the number of bytes of an instruction to be fetched each time another instruction is executed. When a branch instruction is executed, the branch destination information is set in the PC and branched by the following addressing (For details of each instruction, see **CHAPTER 5 EXPLANATION OF INSTRUCTIONS**).

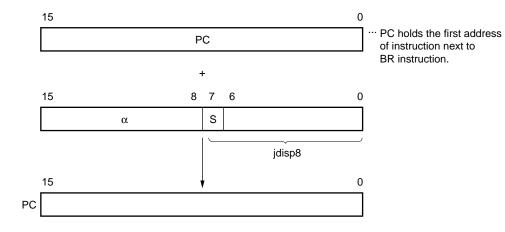

#### 3.1.1 Relative addressing

#### [Function]

The value obtained by adding the 8-bit immediate data (displacement value: jdisp8) of an instruction code to the first address of the following instruction is transferred to the program counter (PC) and program branches. The displacement value is treated as signed two's complement data (–128 to +127) and bit 7 becomes a sign bit. Thus, relative addressing causes a branch to an address within the range of –128 to +127, relative to the first address of the next instruction.

This function is carried out when the BR \$addr16 instruction or a conditional branch instruction is executed.

#### [Illustration]

When S = 0, all bits of  $\alpha$  are 0.

When S = 1, all bits of  $\alpha$  are 1.

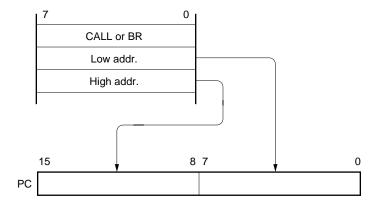

#### 3.1.2 Immediate addressing

#### [Function]

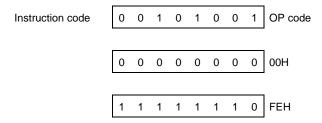

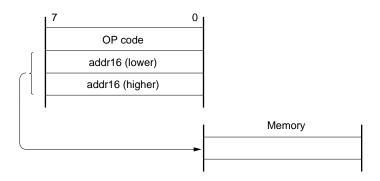

Immediate data in the instruction word is transferred to the program counter (PC) and program branches.

This function is carried out when the CALL !addr16 or BR !addr16 instruction is executed.

The CALL !addr16 and BR !addr16 instructions can be used to branch to any address within the memory spaces.

#### [Illustration]

In case of CALL !addr16 or BR !addr16 instruction

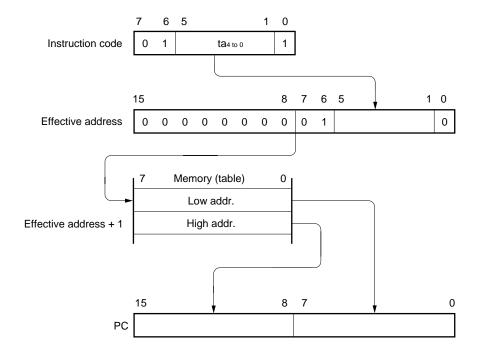

#### 3.1.3 Table indirect addressing

#### [Function]

Table contents (branch destination address) of a particular location, addressed by the immediate data of bits 1 to 5 of an instruction code are transferred to the program counter (PC), and program branches.

Table indirect addressing is performed when the CALLT [addr5] instruction is executed. This instruction references the address stored in the memory table from 40H to 7FH, and allows branching to the entire memory space.

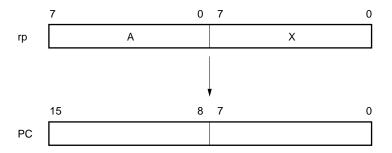

#### 3.1.4 Register addressing

#### [Function]

Register pair (AX) contents specified with an instruction word are transferred to the program counter (PC) and program branches.

This function is carried out when the BR AX instruction is executed.

#### 3.2 Addressing of Operand Address

The following methods are available to specify the register and memory (addressing) which undergo manipulation during instruction execution.

#### 3.2.1 Direct addressing

#### [Function]

This addressing directly addresses a memory to be manipulated with immediate data in an instruction word.

#### [Operand format]

| Operand | Description                    |

|---------|--------------------------------|

| addr16  | Label or 16-bit immediate data |

#### [Description example]

MOV A, !FE00H; When setting !addr16 to FE00H

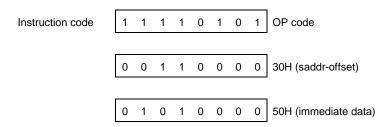

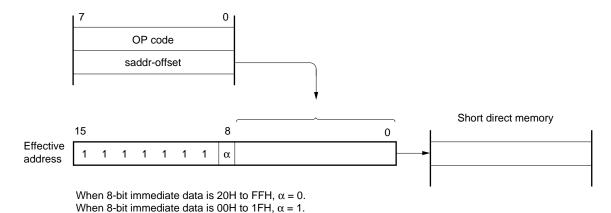

#### 3.2.2 Short direct addressing

#### [Function]

This addressing directly addresses memory to be manipulated in the fixed space with the 8-bit data in an instruction word.

This addressing is applied to the 256-byte fixed space of FE20H to FF1FH. An internal high-speed RAM and special function registers (SFRs) are mapped at FE20H to FEFFH and FF00H to FF1FH, respectively.

The SFR area (FF00H-FF1FH) to which short direct addressing is applied constitutes only part of the overall SFR area. In this area, ports that are frequently accessed in a program and a compare register of the timer/event counter are mapped, and these SFRs can be manipulated with a small number of bytes and clocks.

When 8-bit immediate data is 20H to FFH, bit 8 of an effective address is set to 0. When it is 00H to 1FH, bit 8 is set to 1. See **Illustration** below.

#### [Operand format]

| Operand | Description                                                |

|---------|------------------------------------------------------------|

| saddr   | Label or FE20H to FF1FH immediate data                     |

| saddrp  | Label or FE20H to FF1FH immediate data (even address only) |

#### [Description example]

MOV FE30H, #50H; When setting saddr to FE30H and the immediate data to 50H

#### [Illustration]

User's Manual U11047EJ3V0UM00

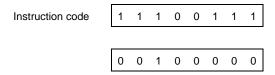

#### 3.2.3 Special function register (SFR) addressing

#### [Function]

This addressing is to address special function registers (SFRs) mapped to the memory with the 8-bit immediate data in an instruction word.

This addressing is applied to the 240-byte spaces of FF00H to FFCFH and FFE0H to FFFFH. However, the SFRs mapped at FF00H to FF1FH can also be accessed by means of short direct addressing.

#### [Operand format]

| Operand | Description                    |

|---------|--------------------------------|

| sfr     | Special function register name |

#### [Description example]

MOV PM0, A; When selecting PM0 for sfr

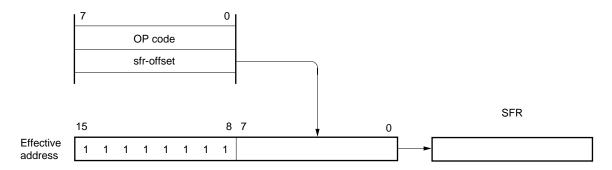

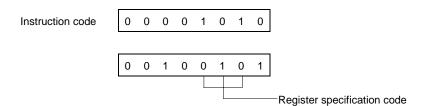

#### 3.2.4 Register addressing

#### [Function]

This addressing is to access a general-purpose register by specifying it as an operand. The general-purpose register to be accessed is specified with a register specification code in an instruction code or function name.

Register addressing is carried out when an instruction with the following operand format is executed. When an 8-bit register is specified, one of the eight registers is specified with 3 bits (register specification code) in the instruction code.

#### [Operand format]

| Operand | Description            |

|---------|------------------------|

| r       | X, A, C, B, E, D, L, H |

| rp      | AX, BC, DE, HL         |

'r' and 'rp' can be described with absolute names (R0 to R7 and RP0 to RP3) as well as functional names (X, A, C, B, E, D, L, H, AX, BC, DE, and HL).

#### [Description example]

MOV A, C; When selecting the C register for r

INCW DE; When selecting the DE register pair for rp

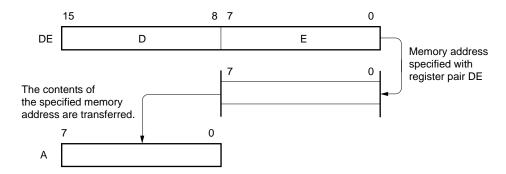

### 3.2.5 Register indirect addressing

## [Function]

This addressing is to address memory using the contents of the special register pair as an operand. The register pair to be accessed is specified with the register pair specification code in an instruction code. This addressing can be carried out for the entire memory space.

### [Operand format]

| Operand | Description |

|---------|-------------|

| _       | [DE], [HL]  |

## [Description example]

MOV A, [DE]; When selecting register pair [DE]

### [Illustration]

#### 3.2.6 Based addressing

### [Function]

This addressing is to address the memory by using the result of adding 8-bit immediate data to the contents of the base register, i.e., the HL register pair. The addition is performed by expanding the offset data as a positive number to 16 bits. A carry from the 16th bit is ignored. This addressing can be carried out for the entire memory space.

### [Operand format]

| Operand | Description |

|---------|-------------|

| _       | [HL + byte] |

#### [Description example]

MOV A, [HL+10H]; When setting "byte" to 10H

### 3.2.7 Stack addressing

### [Function]

This addressing is to indirectly address the stack area with the stack pointer (SP) contents.

This addressing method is automatically employed when the PUSH, POP, subroutine call, or RETURN instructions is executed or when the register is saved/restored upon generation of an interrupt request.

Stack addressing can address the internal high-speed RAM area only.

### [Description example]

In the case of PUSH DE

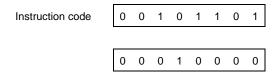

Instruction code 1 0 1 0 1 0 1 0

# **CHAPTER 4 INSTRUCTION SET**

This chapter lists the instruction set of the 78K/0S Series. The instructions are common to all 78K/0S Series products.

### 4.1 Operation

#### 4.1.1 Operand representation and description formats

In the operand column of each instruction, an operand is described according to the description format for operand representation of that instruction (for details, refer to the assembler specifications). When there are two or more description methods, select one of them. Uppercase characters, #, !, \$ and [] are keywords and must be described as is. Each symbol has the following meaning.

#: Immediate data!: Absolute address!: Indirect address[]: Indirect address

In the case of immediate data, describe an appropriate numeric value or a label. When using a label, be sure to describe #, !, \$, or [].

For operand register description formats, r and rp, either functional names (X, A, C, etc.) or absolute names (names in parentheses in the table below, R0, R1, R2, etc.) can be described.

Table 4-1. Operand Representation and Description Formats

| Operand             | Description Format                                                                                                                                                |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r<br>rp<br>sfr      | X (R0), A (R1), C (R2), B (R3), E (R4), D (R5), L (R6), H (R7)  AX (RP0), BC (RP1), DE (RP2), HL (RP3)  Special function register symbol                          |

| saddr<br>saddrp     | FE20H to FF1FH Immediate data or labels FE20H to FF1FH Immediate data or labels (even addresses only)                                                             |

| addr16<br>addr5     | 0000H to FFFFH Immediate data or labels (only even addresses for 16-bit data transfer instructions) 0040H to 007FH Immediate data or labels (even addresses only) |

| word<br>byte<br>bit | 16-bit immediate data or label 8-bit immediate data or label 3-bit immediate data or label                                                                        |

Remark Refer to the User's Manual of each product for symbols of special function registers.

User's Manual U11047EJ3V0UM00

### 4.1.2 Description of operation column

A: A register; 8-bit accumulator

X: X registerB: B registerC: C registerD: D registerE: E registerH: H register

L:

AX: AX register pair; 16-bit accumulator

BC: BC register pair

DE: DE register pair

HL: HL register pair

PC: Program counter

SP: Stack pointer

L register

PSW: Program status word

CY: Carry flag

AC: Auxiliary carry flag

Z: Zero flag

IE: Interrupt request enable flag

NMIS: Non-maskable interrupt servicing flag

(): Memory contents indicated by address or register contents in parentheses

XH, XL: Higher 8 bits and lower 8 bits of 16-bit register

\( \): Logical product (AND)\( \): Logical sum (OR)

: Inverted data

addr16: 16-bit immediate data or label

jdisp8: Signed 8-bit data (displacement value)

## 4.1.3 Description of flag column

(Blank): Not affected 0: Cleared to 0 1: Set to 1

X: Set/cleared according to the resultR: Previously saved value is restored

# 4.1.4 Description of clock column

The number of clock cycles during instruction execution is outlined as follows.

One instruction clock cycle is equal to one CPU clock cycle (fcpu) selected by the processor clock control register (PCC).

The operation list is shown below.

# 4.1.5 Operation list

| Mnemonic | Operand        | Byte | Clock | Operation                       |   | Flag | J  |

|----------|----------------|------|-------|---------------------------------|---|------|----|

|          |                |      |       |                                 |   | AC   | CY |

| MOV      | r, #byte       | 3    | 6     | $r \leftarrow \text{byte}$      |   |      |    |

|          | saddr, #byte   | 3    | 6     | (saddr) ← byte                  |   |      |    |

|          | sfr, #byte     | 3    | 6     | sfr ← byte                      |   |      |    |

|          | A, r           | 2    | 4     | $A \leftarrow r$                |   |      |    |

|          | r, A           | 2    | 4     | $r \leftarrow A$                |   |      |    |

|          | A, saddr       | 2    | 4     | $A \leftarrow (saddr)$          |   |      |    |

|          | saddr, A       | 2    | 4     | (saddr) ← A                     |   |      |    |

|          | A, sfr         | 2    | 4     | A ← sfr                         |   |      |    |

|          | sfr, A         | 2    | 4     | sfr ← A                         |   |      |    |

|          | A, !addr16     | 3    | 8     | A ← (addr16)                    |   |      |    |

|          | !addr16, A     | 3    | 8     | (addr16) ← A                    |   |      |    |

|          | PSW, #byte     | 3    | 6     | PSW ← byte                      | × | ×    | ×  |

|          | A, PSW         | 2    | 4     | $A \leftarrow PSW$              |   |      |    |

|          | PSW, A         | 2    | 4     | PSW ← A                         | × | ×    | ×  |

|          | A, [DE]        | 1    | 6     | $A \leftarrow (DE)$             |   |      |    |

|          | [DE], A        | 1    | 6     | (DE) ← A                        |   |      |    |

|          | A, [HL]        | 1    | 6     | $A \leftarrow (HL)$             |   |      |    |

|          | [HL], A        | 1    | 6     | (HL) ← A                        |   |      |    |

|          | A, [HL + byte] | 2    | 6     | A ← (HL + byte)                 |   |      |    |

|          | [HL + byte], A | 2    | 6     | (HL + byte) ← A                 |   |      |    |

| XCH      | A, X           | 1    | 4     | $A \leftrightarrow X$           |   |      |    |

|          | A, r           | 2    | 6     | $A \leftrightarrow r$           |   |      |    |

|          | A, saddr       | 2    | 6     | $A \leftrightarrow (saddr)$     |   |      |    |

|          | A, sfr         | 2    | 6     | $A \leftrightarrow sfr$         |   |      |    |

|          | A, [DE]        | 1    | 8     | $A \leftrightarrow (DE)$        |   |      |    |

|          | A, [HL]        | 1    | 8     | $A \leftrightarrow (HL)$        |   |      |    |

|          | A, [HL + byte] | 2    | 8     | $A \leftrightarrow (HL + byte)$ |   |      |    |

**Notes 1.** Except r = A.

**2.** Except r = A, X.

**Remark** One instruction clock cycle is equal to one CPU clock (fcpu) cycle selected by the processor clock control register (PCC).

| Mnemonic | Operand        | Byte | Clock | Operation                               |   | Flag | )  |

|----------|----------------|------|-------|-----------------------------------------|---|------|----|

|          |                |      |       |                                         | Z | AC   | CY |

| MOVW     | rp, #word      | 3    | 6     | $rp \leftarrow word$                    |   |      |    |

|          | AX, saddrp     | 2    | 6     | $AX \leftarrow (saddrp)$                |   |      |    |

|          | saddrp, AX     | 2    | 8     | (saddrp) ← AX                           |   |      |    |

|          | AX, rp         | 1    | 4     | $AX \leftarrow rp$                      |   |      |    |

|          | rp, AX         | 1    | 4     | rp ← AX                                 |   |      |    |

| XCHW     | AX, rp         | 1    | 8     | $AX \leftrightarrow rp$                 |   |      |    |

| ADD      | A, #byte       | 2    | 4     | A, CY ← A + byte                        | × | ×    | ×  |

|          | saddr, #byte   | 3    | 6     | (saddr), CY ← (saddr) + byte            | × | ×    | ×  |

|          | A, r           | 2    | 4     | $A, CY \leftarrow A + r$                | × | ×    | ×  |

|          | A, saddr       | 2    | 4     | $A,CY\leftarrow A+(saddr)$              | × | ×    | ×  |

|          | A, !addr16     | 3    | 8     | $A, CY \leftarrow A + (addr16)$         | × | ×    | ×  |

|          | A, [HL]        | 1    | 6     | $A, CY \leftarrow A + (HL)$             | × | ×    | ×  |

|          | A, [HL + byte] | 2    | 6     | $A, CY \leftarrow A + (HL + byte)$      | × | ×    | ×  |

| ADDC     | A, #byte       | 2    | 4     | A, CY ← A + byte + CY                   | × | ×    | ×  |

|          | saddr, #byte   | 3    | 6     | (saddr), CY ← (saddr) + byte + CY       | × | ×    | ×  |

|          | A, r           | 2    | 4     | $A, CY \leftarrow A + r + CY$           | × | ×    | ×  |

|          | A, saddr       | 2    | 4     | A, CY ← A + (saddr) + CY                | × | ×    | ×  |

|          | A, !addr16     | 3    | 8     | $A, CY \leftarrow A + (addr16) + CY$    | × | ×    | ×  |

|          | A, [HL]        | 1    | 6     | $A, CY \leftarrow A + (HL) + CY$        | × | ×    | ×  |

|          | A, [HL + byte] | 2    | 6     | $A, CY \leftarrow A + (HL + byte) + CY$ | × | ×    | ×  |

| SUB      | A, #byte       | 2    | 4     | $A, CY \leftarrow A - byte$             | × | ×    | ×  |

|          | saddr, #byte   | 3    | 6     | $(saddr), CY \leftarrow (saddr) - byte$ | × | ×    | ×  |

|          | A, r           | 2    | 4     | $A, CY \leftarrow A - r$                | × | ×    | ×  |

|          | A, saddr       | 2    | 4     | $A,CY \leftarrow A - (saddr)$           | × | ×    | ×  |

|          | A, !addr16     | 3    | 8     | $A, CY \leftarrow A - (addr16)$         | × | ×    | ×  |

|          | A, [HL]        | 1    | 6     | $A, CY \leftarrow A - (HL)$             | × | ×    | ×  |

|          | A, [HL + byte] | 2    | 6     | A, CY ← A − (HL + byte)                 | × | ×    | ×  |

**Note** Only when rp = BC, DE, or HL.

**Remark** One instruction clock cycle is equal to one CPU clock (fcPu) cycle selected by the processor clock control register (PCC).

| Mnemonic | Operand        | Byte | Clock | Operation                               |   | Fla | g  |

|----------|----------------|------|-------|-----------------------------------------|---|-----|----|

|          |                |      |       |                                         |   | AC  | CY |

| SUBC     | A, #byte       | 2    | 4     | $A, CY \leftarrow A - byte - CY$        | × | ×   | ×  |

|          | saddr, #byte   | 3    | 6     | (saddr), CY ← (saddr) – byte – CY       | × | ×   | ×  |

|          | A, r           | 2    | 4     | $A, CY \leftarrow A - r - CY$           | × | ×   | ×  |

|          | A, saddr       | 2    | 4     | $A,CY\leftarrowA-(saddr)-CY$            | × | ×   | ×  |

|          | A, !addr16     | 3    | 8     | $A, CY \leftarrow A - (addr16) - CY$    | × | ×   | ×  |

|          | A, [HL]        | 1    | 6     | $A,CY \leftarrow A - (HL) - CY$         | × | ×   | ×  |

|          | A, [HL + byte] | 2    | 6     | $A, CY \leftarrow A - (HL + byte) - CY$ | × | ×   | ×  |

| AND      | A, #byte       | 2    | 4     | $A \leftarrow A \land byte$             | × |     |    |

|          | saddr, #byte   | 3    | 6     | (saddr) ← (saddr)∧byte                  | × |     |    |

|          | A, r           | 2    | 4     | $A \leftarrow A \wedge r$               | × |     |    |

|          | A, saddr       | 2    | 4     | $A \leftarrow A \land (saddr)$          | × |     |    |

|          | A, !addr16     | 3    | 8     | $A \leftarrow A \land (addr16)$         | × |     |    |

|          | A, [HL]        | 1    | 6     | $A \leftarrow A \land (HL)$             | × |     |    |

|          | A, [HL + byte] | 2    | 6     | $A \leftarrow A \land (HL + byte)$      | × |     |    |

| OR       | A, #byte       | 2    | 4     | A ← A∨byte                              | × |     |    |

|          | saddr, #byte   | 3    | 6     | $(saddr) \leftarrow (saddr) \lor byte$  | × |     |    |

|          | A, r           | 2    | 4     | $A \leftarrow A \lor r$                 | × |     |    |

|          | A, saddr       | 2    | 4     | $A \leftarrow A \lor (saddr)$           | × |     |    |

|          | A, !addr16     | 3    | 8     | A ← A∨(addr16)                          | × |     |    |

|          | A, [HL]        | 1    | 6     | $A \leftarrow A \lor (HL)$              | × |     |    |

|          | A, [HL + byte] | 2    | 6     | A ← A∨(HL + byte)                       | × |     |    |

| XOR      | A, #byte       | 2    | 4     | A ← A <del>∨</del> byte                 | × |     |    |

|          | saddr, #byte   | 3    | 6     | (saddr) ← (saddr)ybyte                  | × |     |    |

|          | A, r           | 2    | 4     | $A \leftarrow A \forall r$              | × |     |    |